According to the latest announcement from the organization responsible for the standard, the PCI-Express interconnect standard may undergo some significant changes in the coming years.

This morning, PCI-SIG announced the establishment of the PCIe Optical Workgroup, whose responsibility is to focus on implementing PCIe through optical interfaces. The press release also pointed out that the PCI-SIG Optical Workgroup aims to be agnostic to optical technology, supporting a wide range of optical technologies, while potentially developing form factors specific to the technology.

Insight 64 researcher Nathan Brookwood said, "Optical connections will be an important advancement for the PCIe architecture, as they will enable higher performance, lower power consumption, longer reach, and lower latency. Many data-hungry markets and applications, such as cloud and quantum computing, hyperscale data centers, and high-performance computing, will benefit from the PCIe architecture that utilizes optical connections."

PCI-SIG President and Chairman Al Yanes said, "We see the industry showing a keen interest in expanding the coverage of the established multi-generation high-efficiency PCIe technology standard by implementing optical connections between applications." "PCI-SIG welcomes industry input and invites all PCI-SIG members to join the Optical Workgroup, share their expertise, and help set specific workgroup goals and requirements."

Advertisement

Aiming to replace copper interconnects?According to a report by AnandTech, even though the organization is still in its early stages, the impact of traditional copper binding standards could be substantial, as optical technology will bypass some of the increasingly stubborn limitations of copper signal transmission that traditional PCIe is approaching.

PCI-Express was first released in 2000 and was initially developed around the use of high-density edge connectors, which are still in use today. The PCIe card mechanical specification (CEM) defines the form factor of PCIe add-in cards used over the past two decades, ranging from x1 to x16 connections.

Although the PCIe CEM has hardly changed over the years (largely to ensure backward and forward compatibility), the signal standard itself has undergone multiple speed upgrades. Including the latest PCIe 6.0 standard, the speed of a single PCIe channel has increased by 32 times since 2000, and the PCI-SIG will double this speed again in 2025 with PCIe 7.0. Due to the significant increase in the amount of data transmitted per pin, the actual frequency bandwidth used by the standard has also increased to a similar extent, with PCIe 7.0 set to operate at a frequency close to 32GHz.

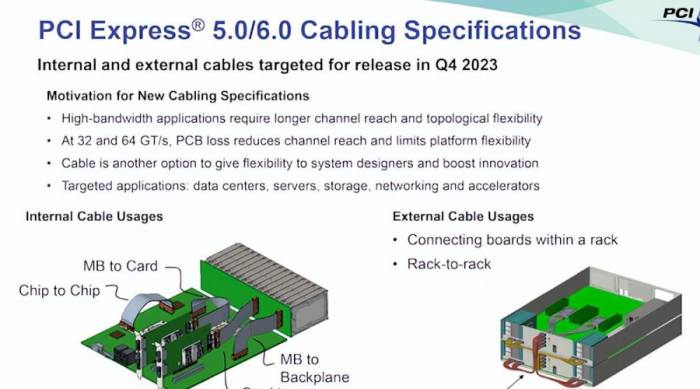

In developing updated PCIe standards, PCI-SIG is committed to minimizing these issues, such as adopting alternative signal transmission methods that do not require higher frequencies (such as PCIe 6 with PAM-4), and using mid-span retimer as the material improves, which helps to keep up with the higher frequencies used by the standard. However, the frequency limitations of copper traces within the PCB have never been completely eliminated, which is why PCI-SIG has established official standards for PCIe based on copper wiring in recent years.The PCIe 5.0/6.0 wiring standards are still in the works by the end of this year, providing options for transferring PCIe using copper cables within the system (internal) and between systems (external). In particular, the relatively thick copper cables have less signal loss compared to PCB traces, overcoming the direct disadvantage of high-frequency communication, which is short channel coverage range (i.e., short signal propagation distance). Although the wiring standard is intended to serve as an alternative to PCIe CEM connectors, not as a large-scale replacement, its existence highlights the problems faced by high-frequency signal transmission over copper cables, which will only become more challenging once PCIe 7.0 is completed.

For this reason, PCI-SIG has established the PCI-SIG Optical Working Group. Like the Ethernet community, which is often at the forefront of high-frequency signal innovation, PCI-SIG also sees optical communication based on light as part of the future of PCIe. As we have seen in optical network technology, optical communication has the potential for longer distances and higher data rates compared to the significant increase in optical frequency, and can reduce power consumption compared to increasingly power-hungry copper wire transmission. For these reasons, PCI-SIG is forming an optical working group to help develop standards required for PCIe through optical connections.

Strictly speaking, driving PCIe through optical connections does not require the creation of new optical standards. Some vendors have already provided proprietary solutions, focusing on external connections. However, the creation of optical standards is precisely for this purpose—standardizing the operation and behavior of PCIe on fiber optics. As part of the working group announcement, the traditionally consensus-based PCI-SIG has made it clear that they will not develop standards for any single optical technology, but instead aim to make it technology-agnostic, allowing the specification to support a wide range of optical technologies.

But PCI-SIG's relatively broad announcement does not just stop at replacing the current copper cables with optical cables. The organization is also considering the "potential development of specific technology form factors." Although the classic CEM connector is unlikely to disappear soon (backward and forward compatibility is very important), the CEM connector is the weakest/most difficult way to provide PCIe today. Therefore, if PCI-SIG is considering new form factors, the optical working group may at least consider some kind of optical-based successor to CEM. If this really becomes a reality, it would easily become the biggest change in the history of the PCIe specification in more than 23 years.It can be affirmed that if any such changes were to occur, it would also take several years. The new optical working group has not yet been formed, let alone setting goals and requirements. The organization has a broad scope of responsibilities aimed at making PCIe more optical-friendly, so it will take a few years before any impact is felt—presumably not earlier than the wiring standards for PCIe 7.0 if it does not have a more direct impact on the PCIe 8.0 specification. However, this indicates the PCI-SIG leadership's view on the future development of the PCIe standard, assuming they can reach a consensus from members. Moreover, although not explicitly stated in the PCI-SIG press release, any serious use of optical PCIe in this way seems to be based on inexpensive optical transceivers (i.e., silicon photonics).

In any case, it will be interesting to see what results the new optical working group of PCI-SIG will eventually produce. As PCIe begins to approach the practical limits of copper, the future of industry standard peripheral interconnects is likely to move towards being lighter.

PCIe 7 at 128GT/s is still the target.

Although the working group is targeting optical interconnects, as introduced in the previous text and the official press release, the existing PCI-SIG working group will continue to move towards the 128GT/s data rate in the PCIe 7.0 specification, while this new optical working group will be committed to making the PCIe architecture more optical-friendly.

According to PCI-SIG, the upcoming PCIe 7.0 specification is planned to be released to members in 2025. The PCIe 7.0 specification is designed to provide a data rate of 128 GT/s, which is twice the data rate of the PCIe 6.0 specification. PCIe 7.0 technology is intended to be a scalable interconnect solution for data-intensive markets such as artificial intelligence/machine learning, data centers, HPC, automotive, IoT, and military/aerospace.According to the press release, the objectives of the PCIe 7.0 specification features include but are not limited to:

- Providing a raw bit rate of 128 GT/s and up to 512 GB/s bidirectional bit rate through an x16 configuration;

- Utilizing PAM4 (4-level Pulse Amplitude Modulation) signaling;

- Focusing on maintaining channel parameters and coverage;

- Continuing to achieve low latency and high reliability goals;

- Enhancing power efficiency;

- Maintaining backward compatibility with all previous generations of PCIe technology.According to the PCI-SIG, they have completed the first draft version 0.3 of the specification and are ready to distribute it to the members of the organization, marking the next step in the development of this standard.

Although the PCI-SIG did not disclose more technical details in the press release, as AnandTech said, the release of the initial draft of the specification marks that the organization has successfully developed the core technology foundation required for faster PCIe communication. And this is not an easy thing, because PCIe 7.0 needs to double the bus frequency at the physical layer, while PCIe 6.0 avoided this major development through PAM4 signaling. But for PCIe 7.0, PCI-SIG can be said to have returned to hard mode development, because it is necessary to improve the physical layer again - this time to make it capable of operating at about 30GHz.

In terms of electrical aspects, PCIe 7.0 adheres to the PAM4 + FLIT encoding, just like its predecessor. Therefore, the next standard will save a lot of effort in the development of the physical layer on the development of the logical layer.

In turn, the compliance program of the specification should be launched and operational in 2027. The compliance program is a barometer of hardware availability, because compliance testing and certification are actually necessary before any large commercial hardware using the new specification can be shipped. With few exceptions, these often take 2 to 2.5 years to complete. All of this indicates that the first commercial PCIe 7.0 products are expected to be released at least by 2027 (five years later), highlighting that there is still a lot of work to be done for PCIe 7.0 after this preliminary draft.A $10 Billion Market

In June, at the 2023 PCI-SIG Developers Conference, PCI-SIG unveiled new findings from an ABI Research report, predicting a compound annual growth rate (CAGR) of 14% for the PCI Express® (PCIe®) technology total addressable market (TAM) from 2022 to 2027. High growth vertical industries include data centers, edge, telecommunications, artificial intelligence, automotive, mobile devices, and wearable devices.

According to this report, the automotive and network edge vertical industries are expected to have the greatest growth opportunities for PCIe technology, with a TAM and CAGR of 53% and 38% respectively during the forecast period. The report suggests that the automotive industry can derive significant value from the widespread adoption of PCIe technology, as it can enable integration in the electrical/electronic (E/E) domain and help systems overcome safety and efficiency challenges in critical mission applications of autonomous vehicles.

The report further points out that high-performance applications such as data centers will contribute to the continued long-term demand for new PCIe technology deployment. In addition to performance, other key drivers for the adoption of PCIe technology include energy efficiency, security, and "time to value."

From the report, we also see that the low power consumption feature (L0p) of the PCIe 6.0 specification will be a major driving force for deployment, as power efficiency becomes a core strategy for adopters who are increasingly focused on sustainability and reducing operational costs; the adoption rate in the AI industry will be high, as PCIe technology provides decision-makers with flexibility through forward and backward compatibility, shortening the time to value and reducing deployment risk; as heterogeneous hardware becomes ubiquitous, complex open radio access network (Open RAN or ORAN) workloads will lead to a continued demand for PCIe technology. Of course, PCIe technology will also perform well in the mobile device vertical, as the rapid development of market innovation will require interconnection of discrete components.ABI Research Research Analyst Reece Hayden said, "In the long term, the demand for PCIe technology will continue to exist as applications requiring faster speeds, embedded security, and higher energy efficiency continue to emerge." "In the short term, this is especially true in the data center and artificial intelligence verticals, as the PCIe 6.0 specification brings more efficient power management features. At the same time, we are seeing a surge in edge heterogeneous computing resources to handle larger datasets and support performance-sensitive applications. The deployment of PCIe technology continues to increase because its high bandwidth and efficiency are very suitable for these challenging computing locations."

PCI-SIG President Al Yanes said, "PCI Express technology, as a foundational I/O interconnect, leads the development of the industry and is widely used in various fields from automotive to data center servers." "This report strongly proves that the future of PCIe technology is bright. As the speed of the PCIe architecture increases, we will continue to expand traditional vertical fields while expanding into exciting new vertical fields to meet the demand for high-bandwidth, low-latency interconnects."

Leave a Comment